- 国内站

- 国际站

无数据

近期,湖南大学刘渊(Yuan Liu)教授通过低温范德华层压(vdW)技术,提出了一种新颖的M3D集成方法,成功解决了传统硅基M3D集成中热预算限制的问题,支持在低温环境下实现多层2D半导体电路的集成。这一方法避免了底层器件性能退化,并展示了在10层大规模2D晶体管集成中的成功应用。此研究为未来具有更多堆叠电路层的M3D器件制备开辟了一条新的途径,展现了其在高密度、低温、多功能集成电路中的广泛应用潜力。该文章以Monolithic three-dimensional tier-by-tier integration via van der Waals lamination为标题发表在Nature上,湖南大学刘渊(Yuan Liu)为本文通讯作者。

文章DOI:https://doi.org/10.1038/s41586-024-07406-z

现有技术缺点

1. 热预算限制:传统的三维单片(Monolithic three-dimensional,M3D)集成由于硅基半导体在高温下制造,而低热预算(通常低于450°C)限制了上层电路的制造工艺温度,阻碍了器件密度的提升和多层集成的发展。

2. 与高能工艺不兼容:二维(2D)半导体材料在微电子学中的应用受限于其与传统高温、高能工艺的不兼容性,尤其是在多层电路集成中,2D材料容易因高温而损坏。

文章亮点

1. 低温范德华层压(vdW)方法:作者提出了一种通过范德华层压技术进行低温M3D集成的方法,将加工温度控制在120°C,有效规避了热预算限制,并在垂直方向上成功实现了多达10个电路层的堆叠集成。

2. 无损多层集成:通过逐层干层压2D半导体电路层的方法,确保了在集成顶层电路时底层2D晶体管性能不受影响,克服了以往集成方法中低层性能退化的问题。

3. 垂直互连与异质结构:利用vdW层间通孔实现不同电路层间的垂直互连和功能集成,使得系统能够实现多种逻辑和异质结构,增强了系统的多功能性。

应用场景

1. 高密度集成电路:该技术适用于开发高密度集成电路,特别是在需要堆叠多个功能层(如逻辑、存储、传感器)的应用中,如高性能计算、智能设备和物联网系统。

2. 低温制造工艺:在对温度敏感的环境中,如柔性电子、可穿戴设备或生物医学设备,该低温集成方法提供了新的制造可能性,确保设备在低温下依然能实现高性能。

3. 新型三维计算系统:该方法支持新型3D计算系统的发展,其中不同功能层能够紧密共存并垂直互连,极大提升了计算系统的性能和集成度。

vdW M3D系统的制备

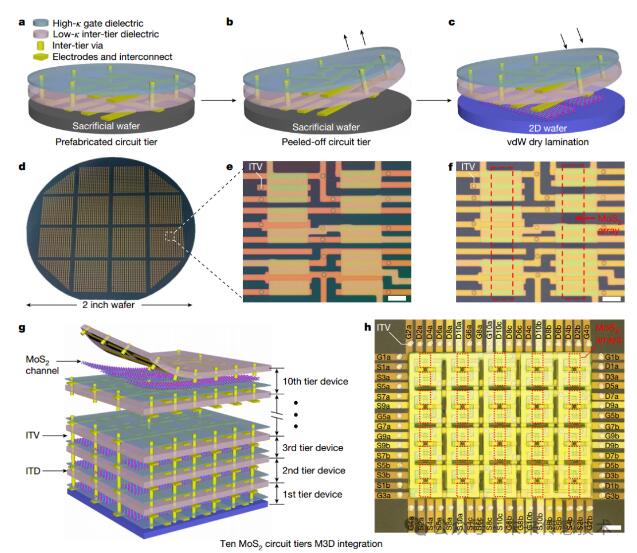

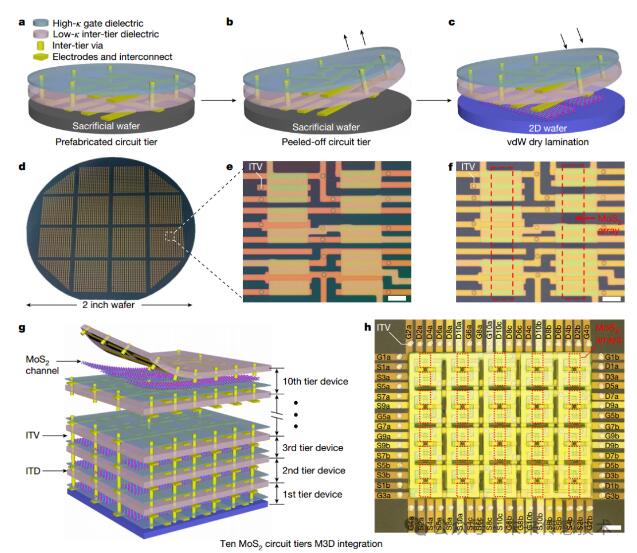

图1a-c展示了vdW集成的详细制备过程。所有电路堆的预制作基于标准光刻工艺,并与晶圆级M3D集成兼容,如图1d- f。

由于层压工艺中的低能量和低温,vdW集成可以重复进行,从而在垂直方向上实现具有多层电路的高密度M3D系统。为了证明这一点,通过将10个化学气相沉积(chemical vapour deposition,CVD)生长的MoS₂层和预制成型的电路层逐层通过vdW堆叠,最终形成一个总厚度约为8μm 的10层M3D电路(图1g,h)。

图1 逐层M3D集成工艺。a-c,M3D集成过程的示意图,包括三个步骤:在牺牲基底上预制电路层(a),物理剥离电路层(b),电路层通过vdW转移技术层压到目标2D表面上(c)。d,e,2英寸牺牲基底上预制电路层的光学图像(d)及其放大图像(e)。f,通过将电路层层压到MoS₂基底上制备的最终器件的光学图像。g,10层M3D系统的示意图。h,对应的10层M3D系统的光学图像。

vdW MoS₂晶体管的测量

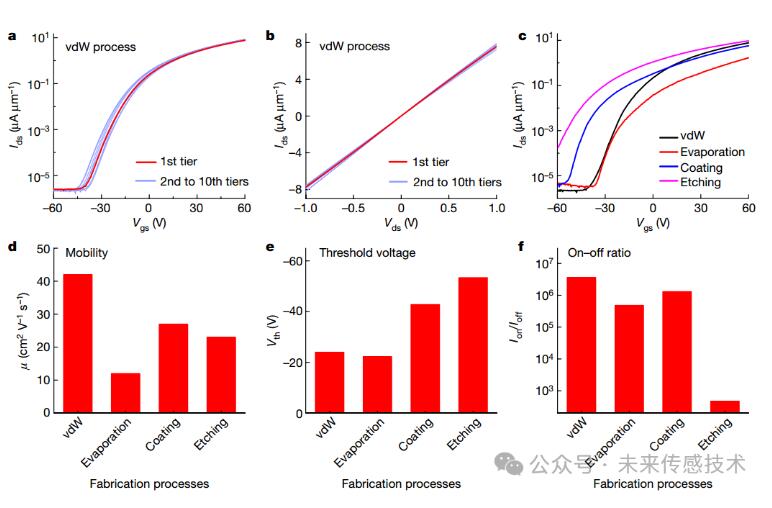

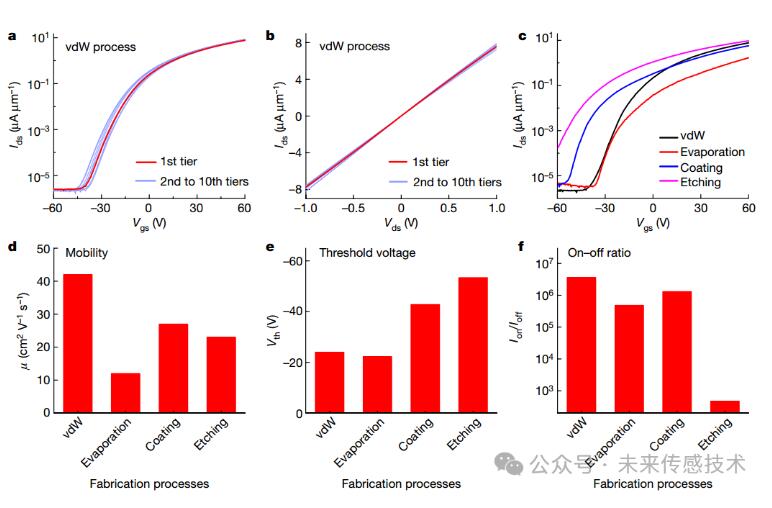

图2 采用不同制备工艺的MoS₂晶体管的电学特性表征。a、b,通过vdW层状堆叠多层电路(1到10层)后底部单层MoS₂晶体管的传输曲线(a)和输出曲线(b),展现出一致的器件性能。c,通过直接在MoS₂沟道上进行各种制备工艺的单层MoS₂晶体管的传输曲线。d-f,通过直接进行各种制备工艺的MoS₂晶体管的载流子迁移率(d)、阈值电压(e)和开关比(f)的总结。在a和c中,偏压为1V,在b中,栅极电压为60V。栅介质为300nm厚的SiO2。Vgs,栅源电压;Vds,漏源电压;Vth,阈值电压;Ion,导通状态电流;Ioff,截止状态电流;Vbg,背栅电压。

M3D通过vdW连接不同层

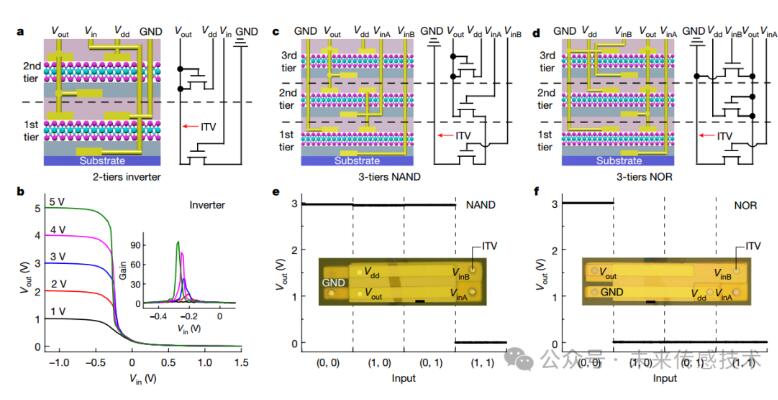

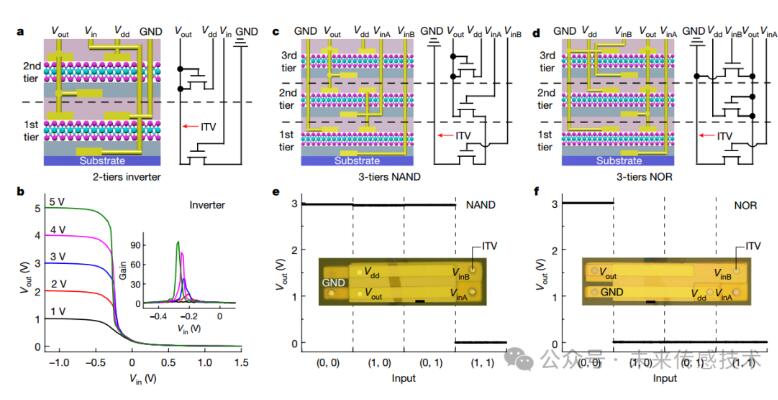

图3 通过多个电路层的vdW M3D集成的逻辑功能。a,由两个不同层中的MoS2晶体管组成的n-型金属-氧化物-半导体反相器的横截面示意图(左)和电路图(右)。b,反相器的电压传输特性和相应的电压增益(插图)随输入电压变化的函数。c,d,由位于三个不同层中的MoS₂晶体管组成的NAND(c)和NOR(d)功能的横截面示意图(左)和电路图(右)。e,f,NAND(e)和NOR(f)电路的输入输出逻辑功能,Vdd为3V。插图是它们对应的光学图像。

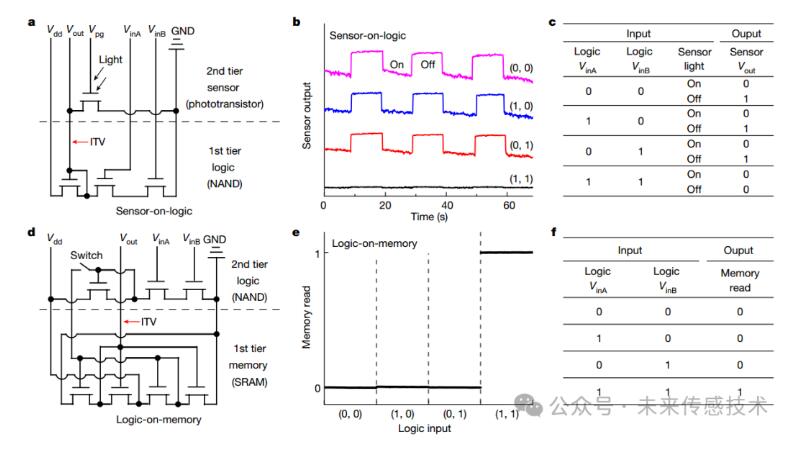

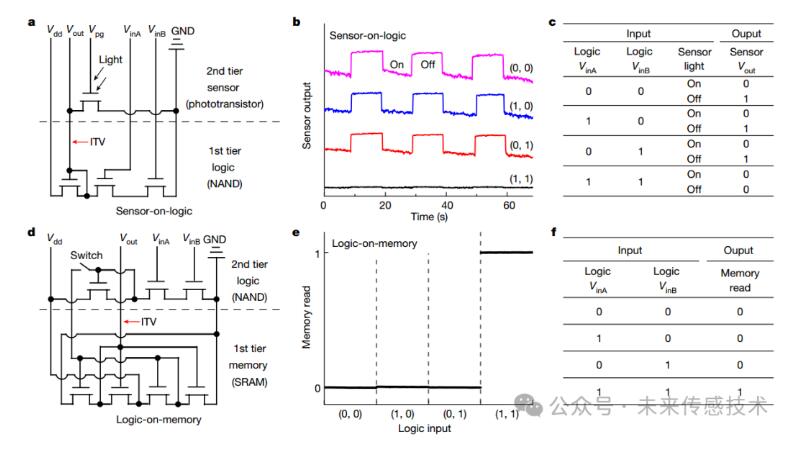

图4 异构M3D集成和垂直互连。a–c,通过vdW M3D集成实现的传感器-逻辑系统的电路图(a),时间相关输出(b)和相应的输入-输出表(c)。d–f,通过vdW M3D集成实现的存储器-逻辑系统的电路图(d),输入-输出特性(e)和相应的输入-输出表(f)。逻辑电路的输出电压通过开关连接到存储电路的输入电压,当开关关闭时应用写入功能,当开关打开时应用存储功能。Vdd为3V。Vpg为光电探测器的栅压。

可扩展基底的M3D集成

这种低温集成工艺也可以应用于以往受到高加工温度或不兼容工艺困扰的非传统电子产品。作者的vdW集成的最高层压温度为120°C,满足PDMS基底的热预算要求。为了证明这一点,作者在室温下通过vdW层压所有逻辑组件(包括接触、栅介质和互连)在PDMS基底上制备了晶体管和逻辑反相器。如扩展数据图12c-e所示,顶部栅极MoS₂晶体管表现出n-型传输行为,具有超过10⁷的高开关比和13 cm² V⁻¹ s⁻¹的载流子迁移率。得到的反相器具有理想的电压传输特性,电压增益为31,表明低温vdW集成没有引入破坏应变,因此对于在各种可拉伸和热膨胀基底上构建高性能无机器件至关重要。

文献来源

Lu, D., Chen, Y., Lu, Z. et al. Monolithic three-dimensional tier-by-tier integration via van der Waals lamination. Nature (2024). https://doi.org/10.1038/s41586-024-07406-z

来源:未来传感技术,FUTURE远见,爱科会易仅用于学术交流

近期,湖南大学刘渊(Yuan Liu)教授通过低温范德华层压(vdW)技术,提出了一种新颖的M3D集成方法,成功解决了传统硅基M3D集成中热预算限制的问题,支持在低温环境下实现多层2D半导体电路的集成。这一方法避免了底层器件性能退化,并展示了在10层大规模2D晶体管集成中的成功应用。此研究为未来具有更多堆叠电路层的M3D器件制备开辟了一条新的途径,展现了其在高密度、低温、多功能集成电路中的广泛应用潜力。该文章以Monolithic three-dimensional tier-by-tier integration via van der Waals lamination为标题发表在Nature上,湖南大学刘渊(Yuan Liu)为本文通讯作者。

文章DOI:https://doi.org/10.1038/s41586-024-07406-z

现有技术缺点

1. 热预算限制:传统的三维单片(Monolithic three-dimensional,M3D)集成由于硅基半导体在高温下制造,而低热预算(通常低于450°C)限制了上层电路的制造工艺温度,阻碍了器件密度的提升和多层集成的发展。

2. 与高能工艺不兼容:二维(2D)半导体材料在微电子学中的应用受限于其与传统高温、高能工艺的不兼容性,尤其是在多层电路集成中,2D材料容易因高温而损坏。

文章亮点

1. 低温范德华层压(vdW)方法:作者提出了一种通过范德华层压技术进行低温M3D集成的方法,将加工温度控制在120°C,有效规避了热预算限制,并在垂直方向上成功实现了多达10个电路层的堆叠集成。

2. 无损多层集成:通过逐层干层压2D半导体电路层的方法,确保了在集成顶层电路时底层2D晶体管性能不受影响,克服了以往集成方法中低层性能退化的问题。

3. 垂直互连与异质结构:利用vdW层间通孔实现不同电路层间的垂直互连和功能集成,使得系统能够实现多种逻辑和异质结构,增强了系统的多功能性。

应用场景

1. 高密度集成电路:该技术适用于开发高密度集成电路,特别是在需要堆叠多个功能层(如逻辑、存储、传感器)的应用中,如高性能计算、智能设备和物联网系统。

2. 低温制造工艺:在对温度敏感的环境中,如柔性电子、可穿戴设备或生物医学设备,该低温集成方法提供了新的制造可能性,确保设备在低温下依然能实现高性能。

3. 新型三维计算系统:该方法支持新型3D计算系统的发展,其中不同功能层能够紧密共存并垂直互连,极大提升了计算系统的性能和集成度。

vdW M3D系统的制备

图1a-c展示了vdW集成的详细制备过程。所有电路堆的预制作基于标准光刻工艺,并与晶圆级M3D集成兼容,如图1d- f。

由于层压工艺中的低能量和低温,vdW集成可以重复进行,从而在垂直方向上实现具有多层电路的高密度M3D系统。为了证明这一点,通过将10个化学气相沉积(chemical vapour deposition,CVD)生长的MoS₂层和预制成型的电路层逐层通过vdW堆叠,最终形成一个总厚度约为8μm 的10层M3D电路(图1g,h)。

图1 逐层M3D集成工艺。a-c,M3D集成过程的示意图,包括三个步骤:在牺牲基底上预制电路层(a),物理剥离电路层(b),电路层通过vdW转移技术层压到目标2D表面上(c)。d,e,2英寸牺牲基底上预制电路层的光学图像(d)及其放大图像(e)。f,通过将电路层层压到MoS₂基底上制备的最终器件的光学图像。g,10层M3D系统的示意图。h,对应的10层M3D系统的光学图像。

vdW MoS₂晶体管的测量

图2 采用不同制备工艺的MoS₂晶体管的电学特性表征。a、b,通过vdW层状堆叠多层电路(1到10层)后底部单层MoS₂晶体管的传输曲线(a)和输出曲线(b),展现出一致的器件性能。c,通过直接在MoS₂沟道上进行各种制备工艺的单层MoS₂晶体管的传输曲线。d-f,通过直接进行各种制备工艺的MoS₂晶体管的载流子迁移率(d)、阈值电压(e)和开关比(f)的总结。在a和c中,偏压为1V,在b中,栅极电压为60V。栅介质为300nm厚的SiO2。Vgs,栅源电压;Vds,漏源电压;Vth,阈值电压;Ion,导通状态电流;Ioff,截止状态电流;Vbg,背栅电压。

M3D通过vdW连接不同层

图3 通过多个电路层的vdW M3D集成的逻辑功能。a,由两个不同层中的MoS2晶体管组成的n-型金属-氧化物-半导体反相器的横截面示意图(左)和电路图(右)。b,反相器的电压传输特性和相应的电压增益(插图)随输入电压变化的函数。c,d,由位于三个不同层中的MoS₂晶体管组成的NAND(c)和NOR(d)功能的横截面示意图(左)和电路图(右)。e,f,NAND(e)和NOR(f)电路的输入输出逻辑功能,Vdd为3V。插图是它们对应的光学图像。

图4 异构M3D集成和垂直互连。a–c,通过vdW M3D集成实现的传感器-逻辑系统的电路图(a),时间相关输出(b)和相应的输入-输出表(c)。d–f,通过vdW M3D集成实现的存储器-逻辑系统的电路图(d),输入-输出特性(e)和相应的输入-输出表(f)。逻辑电路的输出电压通过开关连接到存储电路的输入电压,当开关关闭时应用写入功能,当开关打开时应用存储功能。Vdd为3V。Vpg为光电探测器的栅压。

可扩展基底的M3D集成

这种低温集成工艺也可以应用于以往受到高加工温度或不兼容工艺困扰的非传统电子产品。作者的vdW集成的最高层压温度为120°C,满足PDMS基底的热预算要求。为了证明这一点,作者在室温下通过vdW层压所有逻辑组件(包括接触、栅介质和互连)在PDMS基底上制备了晶体管和逻辑反相器。如扩展数据图12c-e所示,顶部栅极MoS₂晶体管表现出n-型传输行为,具有超过10⁷的高开关比和13 cm² V⁻¹ s⁻¹的载流子迁移率。得到的反相器具有理想的电压传输特性,电压增益为31,表明低温vdW集成没有引入破坏应变,因此对于在各种可拉伸和热膨胀基底上构建高性能无机器件至关重要。

文献来源

Lu, D., Chen, Y., Lu, Z. et al. Monolithic three-dimensional tier-by-tier integration via van der Waals lamination. Nature (2024). https://doi.org/10.1038/s41586-024-07406-z

来源:未来传感技术,FUTURE远见,爱科会易仅用于学术交流

2026.05.15 - 2026.05.18 中国 内蒙古、呼和浩特

2026.05.22 - 2026.05.24 中国 南京

2026.05.29 - 2026.05.31 中国 成都