- 国内站

- 国际站

No data

近日,中国科学院上海微系统与信息技术研究所狄增峰研究员与田子傲研究员展示了利用原子级薄单晶Al₂O₃ (c-Al₂O₃)作为2D FET中高质量顶栅电介质的制造。相关研究成果以题为「Single-crystalline metal-oxide dielectrics for top-gate 2D transistors」发表在最新一期Nature上。

由具有高载流子迁移率的原子级薄材料组成的二维(2D)结构已被研究作为未来晶体管的候选结构。作为组成芯片的基本元件,晶体管的尺寸随着芯片缩小不断接近物理极限,其中发挥着绝缘作用的栅介质材料十分关键,由于缺乏合适的高质量电介质,尽管2D场效应晶体管(FET)具有优异的物理和电学性能,但仍无法发挥其全部理论潜力和优势。

狄增峰研究员(左)与田子傲研究员(右)

电子芯片中的介质材料主要起到绝缘的作用,但当传统的介质材料厚度减小到纳米级别时,其绝缘性能会显著下降,导致电流泄漏。这不仅增加了芯片的能耗,还导致发热量上升,影响了设备的稳定性和使用寿命。为了解决这一难题,中国科学院上海微系统与信息技术研究所狄增峰研究员与田子傲研究员展示了利用原子级薄单晶Al₂O₃(c-Al₂O₃)作为2D FET中高质量顶栅电介质的制造。通过使用插层氧化技术,在室温下在单晶Al表面形成了一层稳定、化学计量且原子级薄的c-Al₂O₃层,厚度为1.25 nm。由于良好的晶体结构和明确定义的界面,c-Al₂O₃的栅极漏电流、界面态密度和介电强度符合国际设备和系统路线图的要求。通过由源极、漏极、介电材料和栅极组成的一步转移工艺,他们实现了顶栅MoS₂ FET,其特点是亚阈值摆幅陡峭,为61 mV dec⁻¹,开/关电流比高,为10⁸,磁滞极小,为10 mV。

该技术和材料展示了生产高质量单晶氧化物的可能性,适合集成到完全可扩展的先进2D FET中,包括负电容晶体管和自旋晶体管。相关研究成果以题为「Single-crystalline metal-oxide dielectrics for top-gate 2D transistors」发表在最新一期Nature上。该项研究成果被央视新闻报道。

值得一提的是,狄增峰研究员2023年就以通讯作者的身份发表了一篇Nature。他们报道了提供了一种制造大规模可折叠硅晶片和柔性太阳能电池的策略。织构化晶体硅晶片总是在晶片边缘区域的表面金字塔之间的尖锐通道处开始破裂。这一事实使他们能够通过钝化边缘区域的金字塔结构来提高硅晶片的柔韧性。这种边缘钝化技术可以商业化生产大规模(>240 cm²)、高效(>24%)的硅太阳能电池,这种电池可以像纸一样卷起来。经过1000次左右弯曲循环后,电池仍能保持100%的功率转换效率。组装成大型(>10000 cm²)柔性模块后,这些电池在-70°C和85°C之间热循环120小时后仍能保持99.62%的功率。此外,当它们连接到软气囊(模拟暴风雨期间的风)上时,暴露在气流中20分钟后仍能保持96.03%的功率。

策略设计

图1a显示了一种无需复杂化学或精密设备即可合成高质量原子级薄c-Al₂O₃层的可扩展方法。以石墨烯(Gr)/锗(Ge)晶圆为模板,采用vdW外延方法通过电子束蒸发制备晶圆级单晶Al。横截面高分辨率透射电子显微镜(HR-TEM)图像和X射线衍射结果如图1所示,以证实单晶Al(111)在单晶上的晶圆级vdW外延GR/Ge(110)。Al可以很容易地从石墨烯上剥离,然后在室温下0.2 ppm的氧气环境中温和地氧化。由于原子级平坦的单晶Al表面和缺氧环境(0.2 ppm O₂),可以实现化学吸附的氧原子的均匀覆盖和有限的氧渗透。在短短几秒钟内,通过逐层机制就形成了厚度为几纳米的超薄c-Al₂O₃层。最后,将原子级薄的c-Al₂O₃转移到诸如SiO₂、MoS₂ 或Au的目标衬底上以制造器件。图1b显示,剥离Al/c-Al₂O₃ 的产率接近100%。剥离的c-Al₂O₃ 薄膜转移到SiO₂ 基底上,横截面HR-TEM图像如图1c所示。Al表面的c-Al₂O₃ 层的厚度约为1.25nm。图1c中红框的放大原子分辨率图像如图1d所示,揭示了Al/ c-Al₂O₃ /SiO₂ 的夹层结构。电子能量损失谱(EEL)图显示了元素分布(图1e),并且Al和O的分布符合夹层结构。此外,可以通过将vdW外延Al层暴露于缺氧环境不同的持续时间来控制c-Al₂O₃ 的厚度(图1f)。图1g显示了击穿场(Ebd)与电流密度趋势的比较。

图1| c-Al₂O₃的制备和表征

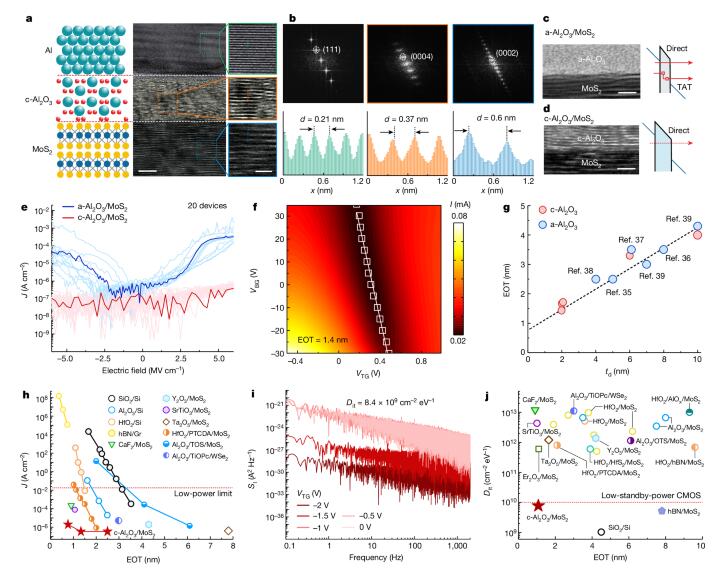

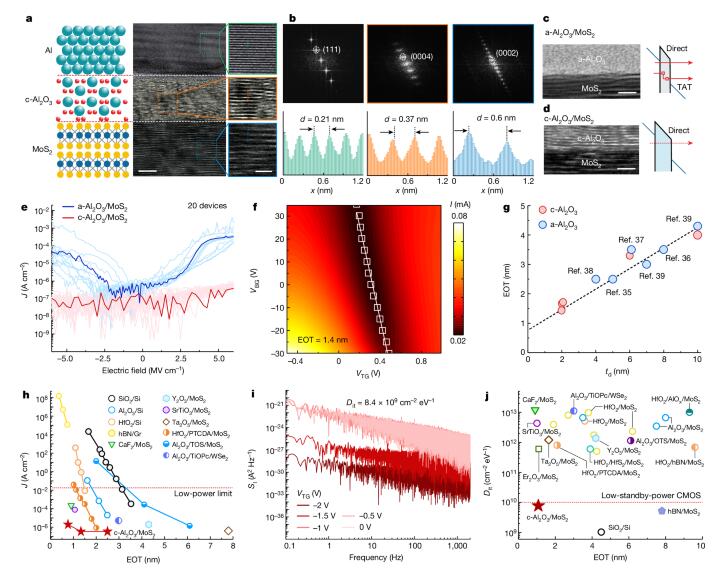

为了确定Al/c-Al₂O₃ 栅极特性,作者将该结构转移到多层MoS₂ 上以形成Al/c-Al₂O₃/MoS₂ 异质结构(图2a)。异质结构的横截面HR-TEM图像显示从上到下分别由单晶Al、c-Al₂O₃ 和MoS₂ 层组成的堆叠。Al、c-Al₂O₃和MoS₂的距离分别为0.21 nm、0.37 nm和0.6 nm(图2b)。通过相同的集成方法将两种不同类型的Al₂O₃ 介电材料(非晶态和晶态)转移到MoS₂ 通道上(图2c-d)。图2e显示了c-Al₂O₃/MoS₂ 和a-Al₂O₃ /MoS₂ 的实验J值,c-Al₂O₃ /MoS₂ 的J值比a-Al₂O₃/MoS₂ 低约两个数量级。作者制作了以SiO₂/Si作为全局背栅、Al/c-Al₂O₃ 作为顶栅叠层的双栅器件,以精确测量等效氧化物厚度 (EOT)。与迄今为止报道的基于Al₂O₃的其他2D器件相比,c-Al₂O₃显示出最小的EOT,并且还展示了缩小2DFET的潜力。

图2| Al/c-Al₂O₃栅极的特性

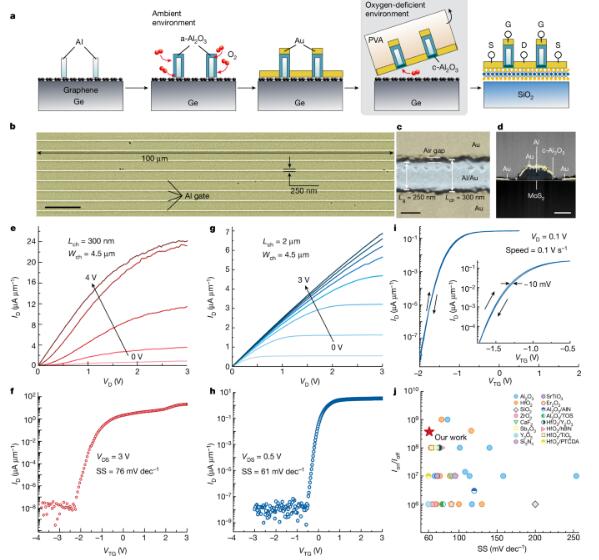

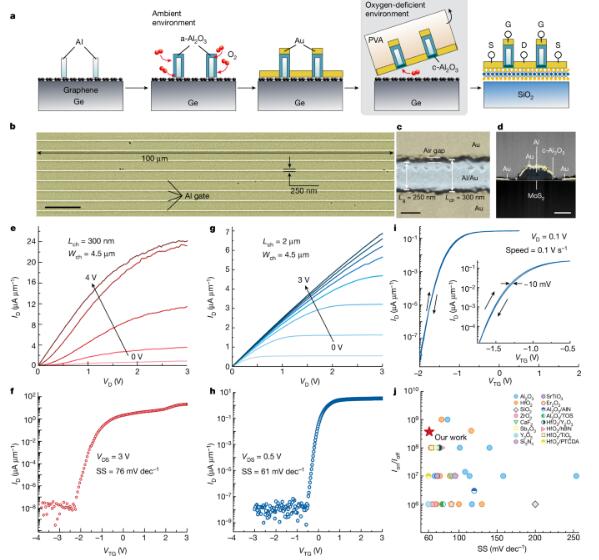

为了研究基于c-Al₂O₃的2D FET的电子特性,采用vdW转移方法制备了具有2 nm c-Al₂O₃的自对准MoS₂ FET。自对准MoS₂ FET的制造工艺如图3a。图3b显示了自对准 MoS₂ FET 阵列的扫描电子显微镜 (SEM) 图像。Al栅极的宽度和长度分别为100μm和250nm。Au和Al栅极之间的小气隙确保了顶栅与源极或漏极之间的完全绝缘以及成功的自对准过程,如图3c所示。自对准MoS₂ FET的横截面TEM图像如图3d所示。vdW转移方法能够通过自对准工艺制造完整的FET堆栈,包括石墨烯/Ge供体晶圆上的源极、漏极、电介质和栅极,然后将其一步转移到沟道材料上层压工艺生产具有良好接触和电介质界面的2D FET。MoS₂ FET的输出(漏极电流与漏极电压,ID–VD)和传输(漏极电流与栅极电压,ID–VTG特性如图3e、f所示。输出特性显示出良好的电流控制和饱和度。

图3| c-Al₂O₃/MoS₂ FET的制造和电子特性

为了进一步证明大面积顶栅FET的可扩展制造,作者在4英寸化学气相沉积(CVD)-MoS₂晶圆上制备了FET阵列。图4a中带有顶栅FET阵列的4英寸CVD-MoS₂/蓝宝石晶圆的照片证实了完整的FET堆栈已转移到MoS₂/蓝宝石衬底上。图4b、c没有显示任何皱纹或裂缝。这些晶体管的典型输出曲线表明,由于采用了高质量的电介质,因此具有出色的沟道静电控制能力(图4d)。100个MoS₂ FET的传输曲线表现出典型的n型特性,具有良好的均匀性(图4e)。从100个器件中提取的开/关电流比(lon/Ioff)和SS的统计分布如图4f所示,以及关键参数的进一步统计分布。

图4|在4英寸CVD-MoS₂ /蓝宝石晶圆上批量制造c-Al₂O₃/MoS₂FET

总结

本文展示了单晶Al₂O₃作为顶栅2D晶体管的高质量介电层的制造。这一突破将为进一步提高单晶氧化物的多样性、可扩展性和可制造性奠定基础,促进2D半导体从实验室到工业环境的无缝过渡。晶圆级单晶铝和氧化铝的生长方法可以进一步扩展到其他金属,并且可以合成一些以前无法获得的单晶氧化物用于各种应用。这一历程中的一个显著进步是能够扩大到当前的硅晶圆直径,因为用于单晶石墨烯合成的起始锗可以直接在硅上外延生长,这大大拓宽了集成到现有硅工厂制造工艺的潜力。同时,开发专用于低维材料(包括单晶介电氧化物、二维通道材料和超薄金属电极)的自动脱键转移工具对于实现多功能二维器件之间独特的对准至关重要,有望大幅提高吞吐量、提高可重复性和增强二维集成电路的可靠性。通过构建复杂的二维集成电路,特别是在成熟的Si-CMOS平台上进行异质集成,二维材料的巨大潜力可以得到充分释放,并为下一代高性能电子设备奠定基础。

来源:高分子科学前沿,FUTURE远见,爱科会易仅用于学术交流

近日,中国科学院上海微系统与信息技术研究所狄增峰研究员与田子傲研究员展示了利用原子级薄单晶Al₂O₃ (c-Al₂O₃)作为2D FET中高质量顶栅电介质的制造。相关研究成果以题为「Single-crystalline metal-oxide dielectrics for top-gate 2D transistors」发表在最新一期Nature上。

由具有高载流子迁移率的原子级薄材料组成的二维(2D)结构已被研究作为未来晶体管的候选结构。作为组成芯片的基本元件,晶体管的尺寸随着芯片缩小不断接近物理极限,其中发挥着绝缘作用的栅介质材料十分关键,由于缺乏合适的高质量电介质,尽管2D场效应晶体管(FET)具有优异的物理和电学性能,但仍无法发挥其全部理论潜力和优势。

狄增峰研究员(左)与田子傲研究员(右)

电子芯片中的介质材料主要起到绝缘的作用,但当传统的介质材料厚度减小到纳米级别时,其绝缘性能会显著下降,导致电流泄漏。这不仅增加了芯片的能耗,还导致发热量上升,影响了设备的稳定性和使用寿命。为了解决这一难题,中国科学院上海微系统与信息技术研究所狄增峰研究员与田子傲研究员展示了利用原子级薄单晶Al₂O₃(c-Al₂O₃)作为2D FET中高质量顶栅电介质的制造。通过使用插层氧化技术,在室温下在单晶Al表面形成了一层稳定、化学计量且原子级薄的c-Al₂O₃层,厚度为1.25 nm。由于良好的晶体结构和明确定义的界面,c-Al₂O₃的栅极漏电流、界面态密度和介电强度符合国际设备和系统路线图的要求。通过由源极、漏极、介电材料和栅极组成的一步转移工艺,他们实现了顶栅MoS₂ FET,其特点是亚阈值摆幅陡峭,为61 mV dec⁻¹,开/关电流比高,为10⁸,磁滞极小,为10 mV。

该技术和材料展示了生产高质量单晶氧化物的可能性,适合集成到完全可扩展的先进2D FET中,包括负电容晶体管和自旋晶体管。相关研究成果以题为「Single-crystalline metal-oxide dielectrics for top-gate 2D transistors」发表在最新一期Nature上。该项研究成果被央视新闻报道。

值得一提的是,狄增峰研究员2023年就以通讯作者的身份发表了一篇Nature。他们报道了提供了一种制造大规模可折叠硅晶片和柔性太阳能电池的策略。织构化晶体硅晶片总是在晶片边缘区域的表面金字塔之间的尖锐通道处开始破裂。这一事实使他们能够通过钝化边缘区域的金字塔结构来提高硅晶片的柔韧性。这种边缘钝化技术可以商业化生产大规模(>240 cm²)、高效(>24%)的硅太阳能电池,这种电池可以像纸一样卷起来。经过1000次左右弯曲循环后,电池仍能保持100%的功率转换效率。组装成大型(>10000 cm²)柔性模块后,这些电池在-70°C和85°C之间热循环120小时后仍能保持99.62%的功率。此外,当它们连接到软气囊(模拟暴风雨期间的风)上时,暴露在气流中20分钟后仍能保持96.03%的功率。

策略设计

图1a显示了一种无需复杂化学或精密设备即可合成高质量原子级薄c-Al₂O₃层的可扩展方法。以石墨烯(Gr)/锗(Ge)晶圆为模板,采用vdW外延方法通过电子束蒸发制备晶圆级单晶Al。横截面高分辨率透射电子显微镜(HR-TEM)图像和X射线衍射结果如图1所示,以证实单晶Al(111)在单晶上的晶圆级vdW外延GR/Ge(110)。Al可以很容易地从石墨烯上剥离,然后在室温下0.2 ppm的氧气环境中温和地氧化。由于原子级平坦的单晶Al表面和缺氧环境(0.2 ppm O₂),可以实现化学吸附的氧原子的均匀覆盖和有限的氧渗透。在短短几秒钟内,通过逐层机制就形成了厚度为几纳米的超薄c-Al₂O₃层。最后,将原子级薄的c-Al₂O₃转移到诸如SiO₂、MoS₂ 或Au的目标衬底上以制造器件。图1b显示,剥离Al/c-Al₂O₃ 的产率接近100%。剥离的c-Al₂O₃ 薄膜转移到SiO₂ 基底上,横截面HR-TEM图像如图1c所示。Al表面的c-Al₂O₃ 层的厚度约为1.25nm。图1c中红框的放大原子分辨率图像如图1d所示,揭示了Al/ c-Al₂O₃ /SiO₂ 的夹层结构。电子能量损失谱(EEL)图显示了元素分布(图1e),并且Al和O的分布符合夹层结构。此外,可以通过将vdW外延Al层暴露于缺氧环境不同的持续时间来控制c-Al₂O₃ 的厚度(图1f)。图1g显示了击穿场(Ebd)与电流密度趋势的比较。

图1| c-Al₂O₃的制备和表征

为了确定Al/c-Al₂O₃ 栅极特性,作者将该结构转移到多层MoS₂ 上以形成Al/c-Al₂O₃/MoS₂ 异质结构(图2a)。异质结构的横截面HR-TEM图像显示从上到下分别由单晶Al、c-Al₂O₃ 和MoS₂ 层组成的堆叠。Al、c-Al₂O₃和MoS₂的距离分别为0.21 nm、0.37 nm和0.6 nm(图2b)。通过相同的集成方法将两种不同类型的Al₂O₃ 介电材料(非晶态和晶态)转移到MoS₂ 通道上(图2c-d)。图2e显示了c-Al₂O₃/MoS₂ 和a-Al₂O₃ /MoS₂ 的实验J值,c-Al₂O₃ /MoS₂ 的J值比a-Al₂O₃/MoS₂ 低约两个数量级。作者制作了以SiO₂/Si作为全局背栅、Al/c-Al₂O₃ 作为顶栅叠层的双栅器件,以精确测量等效氧化物厚度 (EOT)。与迄今为止报道的基于Al₂O₃的其他2D器件相比,c-Al₂O₃显示出最小的EOT,并且还展示了缩小2DFET的潜力。

图2| Al/c-Al₂O₃栅极的特性

为了研究基于c-Al₂O₃的2D FET的电子特性,采用vdW转移方法制备了具有2 nm c-Al₂O₃的自对准MoS₂ FET。自对准MoS₂ FET的制造工艺如图3a。图3b显示了自对准 MoS₂ FET 阵列的扫描电子显微镜 (SEM) 图像。Al栅极的宽度和长度分别为100μm和250nm。Au和Al栅极之间的小气隙确保了顶栅与源极或漏极之间的完全绝缘以及成功的自对准过程,如图3c所示。自对准MoS₂ FET的横截面TEM图像如图3d所示。vdW转移方法能够通过自对准工艺制造完整的FET堆栈,包括石墨烯/Ge供体晶圆上的源极、漏极、电介质和栅极,然后将其一步转移到沟道材料上层压工艺生产具有良好接触和电介质界面的2D FET。MoS₂ FET的输出(漏极电流与漏极电压,ID–VD)和传输(漏极电流与栅极电压,ID–VTG特性如图3e、f所示。输出特性显示出良好的电流控制和饱和度。

图3| c-Al₂O₃/MoS₂ FET的制造和电子特性

为了进一步证明大面积顶栅FET的可扩展制造,作者在4英寸化学气相沉积(CVD)-MoS₂晶圆上制备了FET阵列。图4a中带有顶栅FET阵列的4英寸CVD-MoS₂/蓝宝石晶圆的照片证实了完整的FET堆栈已转移到MoS₂/蓝宝石衬底上。图4b、c没有显示任何皱纹或裂缝。这些晶体管的典型输出曲线表明,由于采用了高质量的电介质,因此具有出色的沟道静电控制能力(图4d)。100个MoS₂ FET的传输曲线表现出典型的n型特性,具有良好的均匀性(图4e)。从100个器件中提取的开/关电流比(lon/Ioff)和SS的统计分布如图4f所示,以及关键参数的进一步统计分布。

图4|在4英寸CVD-MoS₂ /蓝宝石晶圆上批量制造c-Al₂O₃/MoS₂FET

总结

本文展示了单晶Al₂O₃作为顶栅2D晶体管的高质量介电层的制造。这一突破将为进一步提高单晶氧化物的多样性、可扩展性和可制造性奠定基础,促进2D半导体从实验室到工业环境的无缝过渡。晶圆级单晶铝和氧化铝的生长方法可以进一步扩展到其他金属,并且可以合成一些以前无法获得的单晶氧化物用于各种应用。这一历程中的一个显著进步是能够扩大到当前的硅晶圆直径,因为用于单晶石墨烯合成的起始锗可以直接在硅上外延生长,这大大拓宽了集成到现有硅工厂制造工艺的潜力。同时,开发专用于低维材料(包括单晶介电氧化物、二维通道材料和超薄金属电极)的自动脱键转移工具对于实现多功能二维器件之间独特的对准至关重要,有望大幅提高吞吐量、提高可重复性和增强二维集成电路的可靠性。通过构建复杂的二维集成电路,特别是在成熟的Si-CMOS平台上进行异质集成,二维材料的巨大潜力可以得到充分释放,并为下一代高性能电子设备奠定基础。

来源:高分子科学前沿,FUTURE远见,爱科会易仅用于学术交流