- 国内站

- 国际站

No data

三维集成是通过在垂直方向上将多个独立的芯片或功能层堆叠在一起的器件系统,能够实现逻辑、存储和传感等功能的垂直集成和协同工作,是后摩尔时代的重要技术路线。目前商用的三维集成主要是通过封装技术将多芯片或者多芯粒垂直堆叠和互联。单芯片三维集成则是直接在同一芯片内部垂直集成多个器件层。通过将每一器件层直接制备在另一器件层之上,能够进一步提高芯片的互联密度和性能。然而,硅基单芯片三维集成面临着严重的热预算问题,其上层的硅沟道制备工艺会导致下层硅器件掺杂扩散和性能退化,限制了三维集成的发展。

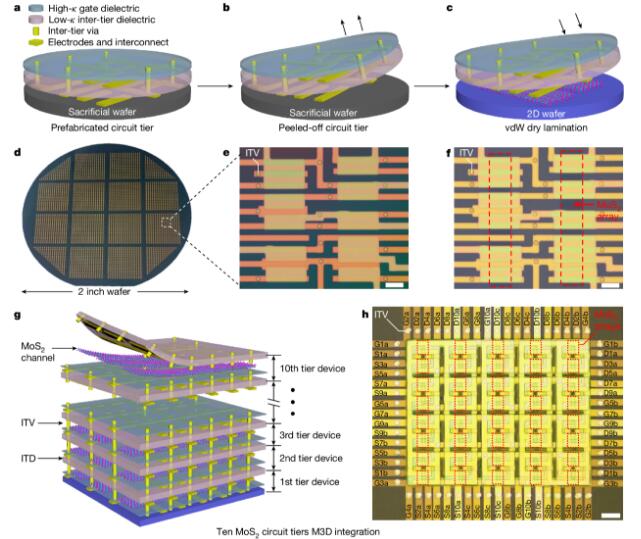

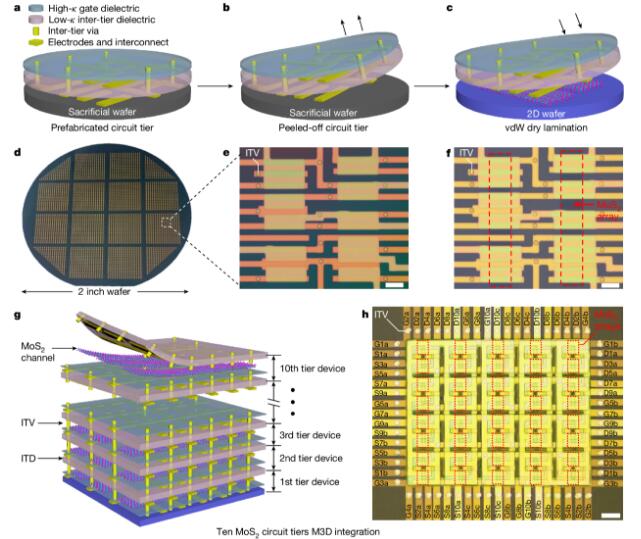

针对这一挑战,湖南大学物理与微电子科学学院刘渊教授团队报道了一种低温的范德华单芯片三维集成工艺。在该工艺中,源/漏/栅电极、层内互连金属、高κ栅介电质、低κ层间介电层和层间垂直通孔等电路功能层首先预制备在牺牲晶圆上,之后在120 °C的低温下范德华集成到半导体晶圆上。通过逐层集成范德华预制备电路层和半导体层,团队实现了10层的全范德华单芯片三维系统。同时,团队发现范德华集成工艺不会对底部的硫化钼晶体管电学性能产生影响,能够保证晶体管的本征性能。进一步集成不同功能的电路层,团队实现了逻辑、传感和存储互联的三维异质集成和协同工作。该研究为单芯片三维集成系统提供了一条低能量路径。

5月22日,该研究成果以「Monolithic three-dimensional tier-by-tier integration via van der Waals lamination」为题在线发表在《自然》杂志上,湖南大学为独立完成单位,作者分别来自湖南大学物电院、化工院、半导体学院。湖南大学物电院陆冬林博士为第一作者,物电院刘渊教授为唯一通讯作者。该工作得到了来自国家自然科学基金、国家重点研发计划等项目的资助。

论文链接:

https://www.nature.com/articles/s41586-024-07406-z

来源:湖南大学,爱科会易仅用于学术交流

三维集成是通过在垂直方向上将多个独立的芯片或功能层堆叠在一起的器件系统,能够实现逻辑、存储和传感等功能的垂直集成和协同工作,是后摩尔时代的重要技术路线。目前商用的三维集成主要是通过封装技术将多芯片或者多芯粒垂直堆叠和互联。单芯片三维集成则是直接在同一芯片内部垂直集成多个器件层。通过将每一器件层直接制备在另一器件层之上,能够进一步提高芯片的互联密度和性能。然而,硅基单芯片三维集成面临着严重的热预算问题,其上层的硅沟道制备工艺会导致下层硅器件掺杂扩散和性能退化,限制了三维集成的发展。

针对这一挑战,湖南大学物理与微电子科学学院刘渊教授团队报道了一种低温的范德华单芯片三维集成工艺。在该工艺中,源/漏/栅电极、层内互连金属、高κ栅介电质、低κ层间介电层和层间垂直通孔等电路功能层首先预制备在牺牲晶圆上,之后在120 °C的低温下范德华集成到半导体晶圆上。通过逐层集成范德华预制备电路层和半导体层,团队实现了10层的全范德华单芯片三维系统。同时,团队发现范德华集成工艺不会对底部的硫化钼晶体管电学性能产生影响,能够保证晶体管的本征性能。进一步集成不同功能的电路层,团队实现了逻辑、传感和存储互联的三维异质集成和协同工作。该研究为单芯片三维集成系统提供了一条低能量路径。

5月22日,该研究成果以「Monolithic three-dimensional tier-by-tier integration via van der Waals lamination」为题在线发表在《自然》杂志上,湖南大学为独立完成单位,作者分别来自湖南大学物电院、化工院、半导体学院。湖南大学物电院陆冬林博士为第一作者,物电院刘渊教授为唯一通讯作者。该工作得到了来自国家自然科学基金、国家重点研发计划等项目的资助。

论文链接:

https://www.nature.com/articles/s41586-024-07406-z

来源:湖南大学,爱科会易仅用于学术交流